## GUJARAT TECHNOLOGICAL UNIVERSITY

M. E. - SEMESTER – II • EXAMINATION – SUMMER • 2013

| Subject code: 1724202 Date: 31-05-2013 |            |                                                                                                                                                      |          |  |

|----------------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|

|                                        |            | t Name: Testing and Verification of VLSI Design                                                                                                      |          |  |

|                                        |            | 10.30 am – 01.00 pm Total Marks: 70                                                                                                                  |          |  |

| Ins                                    |            | ctions:<br>. Attempt all questions.                                                                                                                  |          |  |

|                                        | 2          | <ul> <li>Make suitable assumptions wherever necessary.</li> <li>Figures to the right indicate full marks.</li> </ul>                                 |          |  |

|                                        | 3.         | . Figures to the right indicate full marks.                                                                                                          |          |  |

| Q.1                                    | (a)<br>(b) | Write a test bench for 4 to 1 MUX.  Justify significance of code coverage and functional coverage.                                                   | 07<br>07 |  |

| Q.2                                    | (a)<br>(b) | Describe the need for scan chain and explain how it will be implemented? Write in Brief: i) Design for verification ii)Verification Reuse.           | 07<br>07 |  |

|                                        |            | OR                                                                                                                                                   |          |  |

|                                        | <b>(b)</b> | Write in Brief: i) Reconvergence model ii) Verification of reusable components.                                                                      | 07       |  |

| Q.3                                    | (a)        | Explain various verification methodologies. Which verification methodology you will choose after clock tree insertion?                               | 07       |  |

|                                        | <b>(b)</b> | Writ the difference between  i) Simulator and emulator  ii) Third Party Model and Hardware modeler  iii) Cycle based and event Driven Simulation  OR | 07       |  |

| Q.3                                    | (a)        | Explain In Brief:                                                                                                                                    | 07       |  |

| •                                      | ()         | i) Fault Equivalence ii) Controllability                                                                                                             |          |  |

|                                        |            | iii) Observabillity iv) Fault Masking                                                                                                                |          |  |

|                                        |            | v) Redundant fault vi) Pattern Sensitive Fault vii) On line testing                                                                                  |          |  |

|                                        | <b>(b)</b> | i) Why fault modeling at logical level is more preferred?                                                                                            | 07       |  |

|                                        |            | ii) Though test generation of multiple faults is possible why it is not attempted commonly?                                                          |          |  |

| <b>Q.4</b>                             | (a)        | Explain the stuck open fault for transistor with necessary example.                                                                                  | 07       |  |

|                                        | <b>(b)</b> | For a CMOS implementation of NAND gate find out the complete test vector set for all the transistors are stuck open or stuck short.                  | 07       |  |

|                                        |            | OR                                                                                                                                                   |          |  |

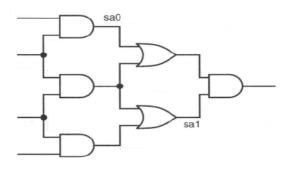

| Q.4                                    | (a)        | For a gate level implementation given below Find out i) Total number of faults                                                                       | 07       |  |

|                                        |            | ii) Apply fault dominance and fault equivalence and find out fault collapsing ratio.                                                                 |          |  |

|                                        |            | iii) list out the test set for faults shown in fig.                                                                                                  |          |  |

|     | <b>(b)</b> | For a gate level implementation of XOR gate only using NAND gate i) Calculate controllability at each net of the implementation ii) Find out Observability at each net. | 07       |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Q.5 | (a)<br>(b) | List out various adhoc DFT techniques and explain any two of them in brief. Explain concept of random access scan.                                                      | 07<br>07 |

| Q.5 | (a)        | OR What if roll of LFSR in Bist?                                                                                                                                        | 07       |

|     | <b>(b)</b> | What is the significance of ATPG?                                                                                                                                       | 07       |

\*\*\*\*\*