## GUJARAT TECHNOLOGICAL UNIVERSITY M. E. - SEMESTER – I • EXAMINATION – WINTER • 2013

Subject Code: 712602N Date: 26-12-2013

Subject Name: CMOS Circuit Design-I

Time: 10.30 am – 01.00 pm Total Marks: 70

**Instructions:**

- 1. Attempt all questions.

- 2. Make suitable assumptions wherever necessary.

- 3. Figures to the right indicate full marks.

- Q.1 (a) Draw the equivalent CMOS inverter circuit for Low to High transition and high to low transition. Also prove that if CMOS inverter is switched ON and OFF f times per second, the dynamic power consumption is

$$Pdyn = C_L V_{DD}^2 f$$

- (b) Discuss importance and impact of scaling in VLSI and compare full scaling 07 and fixed voltage scaling in detail.

- Q.2 (a) Discuss Manchester carry –chain adder. 07

- (b) Explain carry save multiplier. 07

## OR

- (b) Discuss Dynamic Threshold scaling (DTS) to reduce power consumption. 07

- Q.3 (a) Draw source follower circuit and its small signal equivalent circuit. Derive 07 voltage gain  $A_V$  and output resistance  $R_{OUT}$ .

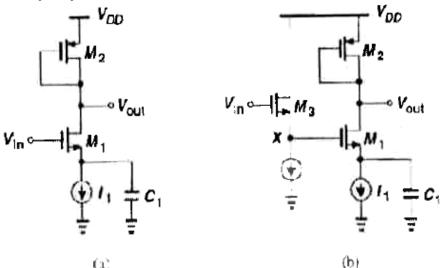

- (b) As shown in circuit (a), calculate the voltage gain if C1 acts as an ac short at 07 the frequency of interest.

- I) What is the maximum dc level of the input signal for which M1 remains saturated?

- II) To accommodate an input dc level close to Vdd, the circuit is modified as shown in (b). What relationship among the gate source voltages of M1-M3 guarantees that M1 is saturated?

OR

- Q.3 (a) Discuss Multipole Systems for stability and frequency compensation.. 07

- (b) Explain any two second order effects in detail.

| <b>Q.4</b> | (a)        | Discuss Gilbert cell Why Gilbert cell consumes a greater voltage headroom | 07        |

|------------|------------|---------------------------------------------------------------------------|-----------|

|            |            | than a simple differential pair?                                          |           |

|            | <b>(b)</b> | Discuss Qualitative analysis of differential pair.                        | <b>07</b> |

|            |            | OR                                                                        |           |

| Q.4        | (a)        | Discuss frequency response of common source stage.                        | <b>07</b> |

|            | <b>(b)</b> | Draw high –frequency model of a cascade stage and explain.                | 07        |

| Q.5        | (a)        | Explain the following:                                                    | 07        |

|            | ` /        | (1) Basics of current mirror                                              |           |

|            |            | (2) Folded cascode                                                        |           |

|            | <b>(b)</b> | Discuss basic cascode current mirrors.                                    | 07        |

|            |            | OR                                                                        |           |

| Q.5        | (a)        | Discuss simple op-amp topologies and cascade op-amps in brief.            | 07        |

|            | <b>(b)</b> | Discuss following performance parameters of op-amp:                       | 07        |

|            |            | (1) Small Signal Bandwidth                                                |           |

|            |            | (2) Large Signal Bandwidth                                                |           |

|            |            | (3) Output Swing                                                          |           |

|            |            | \                                                                         |           |

\*\*\*\*\*